# **SMART STACKS IN VHDL**

EuroForth 2020 Andrew Read, Ulli Hoffmann

#### WHY VHDL AT EUROFORTH?

# SOFTWARE

C

HARDWARECPU, MCU

Do you prefer a hard or soft boundary?

SOFTWARE

• FORTH

HARDWAREFPGA (VHDL)

"Delegate to the hardware"

<sup>\*&</sup>quot;Delegate to the hardware" concept credit Klaus Schleisiek and Microcore

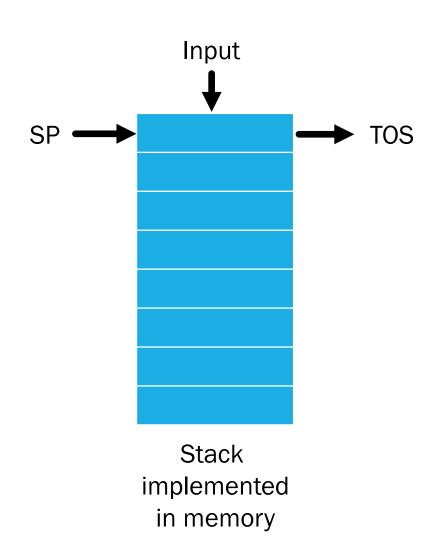

#### A STACK AS MEMORY

```

entity stack 1 is

generic(width : natural;

depth : natural );

port( clk : in std_logic;

rst : in std_logic;

input : in std_logic_vector(width - 1 downto 0);

stack_pointer_n : in integer range 0 to depth - 1;

write enable : in std logic;

output : out std logic vector(width - 1 downto 0);

10

stack pointer : out integer range 0 to depth - 1

11

12

end entity;

```

#### A STACK WITH OPERATIONS

```

entity stack 2 is

16

generic(width : natural;

17

depth : natural );

18

port( clk : in std logic;

19

rst : in std_logic;

20

input : in std_logic_vector(width - 1 downto 0);

stack op : in stack_op_type;

21

22

output : out std logic vector(width - 1 downto 0);

23

stack pointer : out integer range 0 to depth - 1;

24

err under : out std logic;

25

err over : out std logic

26

27

end entity;

28

29

type stack op type is

30

(s_nop, s_push, s_drop, s_replace, s_reset);

```

## **INSIDE THE ARCHITECTURE**

```

33

case stack_op is

34

when s_push =>

we <= '1'; sp_n <= sp_inc;

35

36

37

-- other cases

38

39

when s_nop =>

40

we <= '0'; sp_n <= sp;

41

42

end case;

43

```

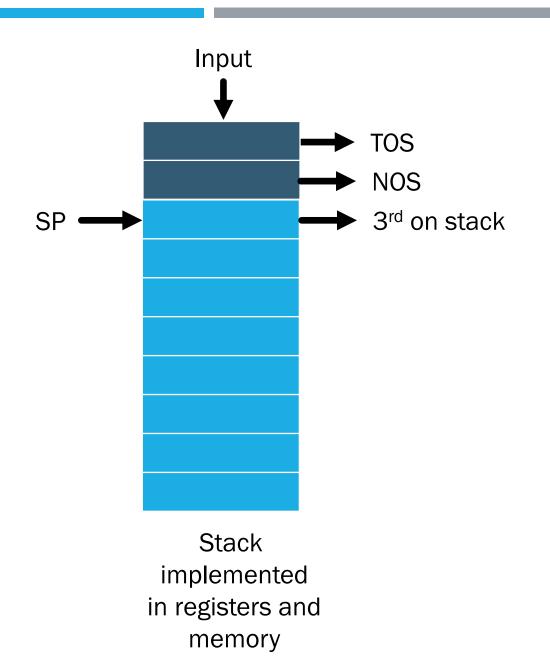

## **AUGMENTING WITH REGISTERS**

## **SOME MORE OPERATIONS**

#### A SMART STACK

```

entity stack 3 is

46

generic(width : natural;

47

depth : natural );

48

port( clk : in std_logic;

49

rst : in std_logic;

input : in std_logic_vector(width - 1 downto 0);

50

51

stack_op : in stack_op_type;

52

tos : out std logic vector(width - 1 downto 0);

53

nos : out std logic vector(width - 1 downto 0);

54

stack pointer : out integer range 0 to depth - 1;

55

err under : out std logic;

56

err over : out std logic

57

);

58

end entity;

```

#### **EXCEPTION HANDLING?**

- CATCH and THROW necessitate special stack handling

- Typical software implementations rely on hooks for reading and writing the stack pointers

- But...

- This breaks the hardware abstraction

- Can we delegate exception handling to hardware?

#### A STACK WITH TWO STACKS INSIDE

```

entity stack_3 is

46

generic(width : natural;

depth : natural );

48

port( clk : in std logic;

rst : in std logic;

50

input : in std logic vector(width - 1 downto 0);

51

stack op : in stack op type;

tos : out std logic vector(width - 1 downto 0);

nos : out std logic vector(width - 1 downto 0);

entity stack_1 is

55

2

generic(width : natural;

56

depth : natural );

port( clk : in std_logic;

rst : in std_logic;

input : in std_logic_vector(width - 1 downto 0);

stack_pointer_n : in integer range 0 to depth - 1;

8

write_enable : in std_logic;

9

output : out std_logic_vector(width - 1 downto 0);

10

stack_pointer : out integer range 0 to depth - 1

11

12

end entity;

```

```

entity stack 2 is

16

generic(width : natural;

17

depth : natural );

18

port( clk : in std logic;

rst : in std_logic;

input : in std_logic_vector(width - 1 downto 0);

stack_op : in stack_op_type;

output : out std_logic_vector(width - 1 downto 0);

stack pointer : out integer range 0 to depth - 1;

err under : out std logic;

err over : out std logic

26

end entity;

```

## **OPERATIONS FOR EXCEPTION HANDLING**

```

s_saveSP, s_restoreSP, s_dropS

s_saveSPAndPush, s_restoreSPAndPush, s_dropSPAndDrop

```

# **RECOMMENDATION:** vhdlwhiz.com

# **BRIEF DEMONSTRATION!**

#### **CONCLUSION**

We have developed a smart stack approach to hardware stacks in VDHL which focuses on abstraction and scalability.

Two smart stacks, encapsulated as a single entity, provide simple exception handling.

This work is a spin-off of our research and development in seedForth.

Ulrich Hoffmann (FH Wedel University of Applied Sciences), uh@fh-wedel.de

Andrew Read andrew81244@outlook.com